HBM SoC Physical Design Engineer

150 jobs found — updated daily

As a SoC Physical Design Engineer in the Heterogeneous Integration Group (HIG), you will drive the implementation of advanced HBM SoC logic/base die designs from netlist to GDSII. You will work closely with RTL design, verification, DFT, IP providers, packaging/assembly, and manufacturing teams to deliver best‑in‑class PPA (performance, power, area) and robust signoff collateral for tape-out. This is a hands‑on role with opportunities to own blocks or top‑level integration across multiple product generations.

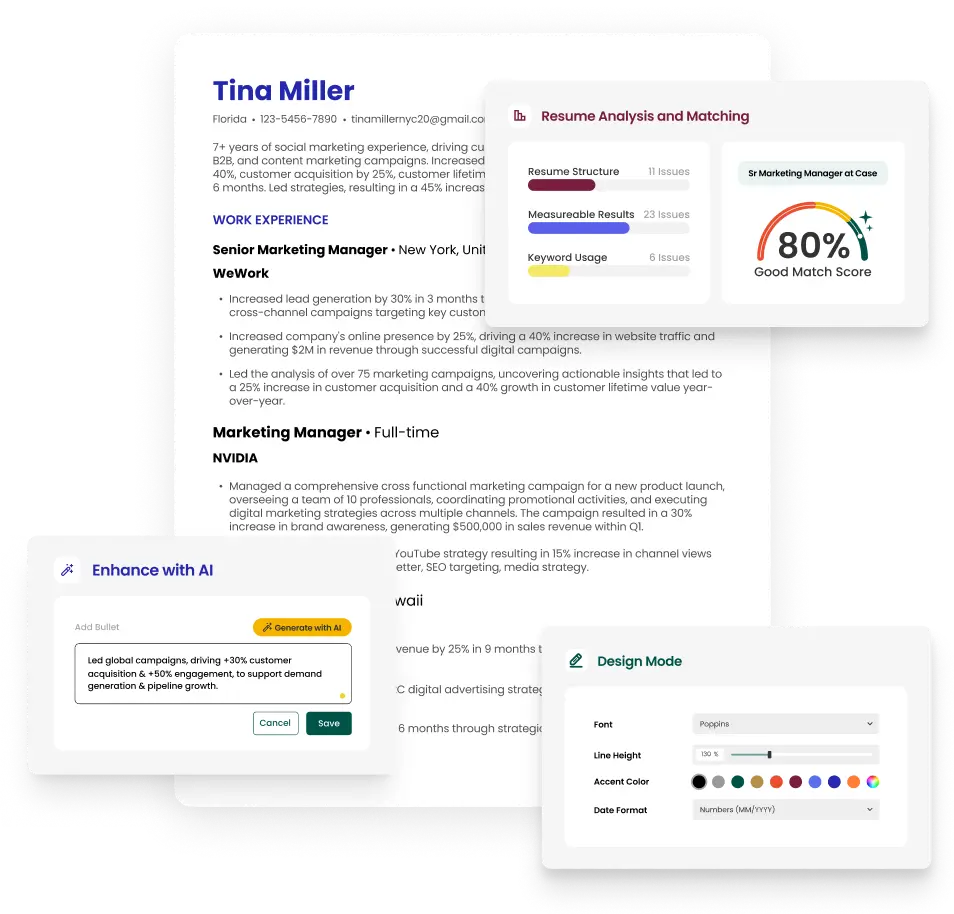

Stand Out From the Crowd

Upload your resume and get instant feedback on how well it matches this job.

Job Type

Full-time

Career Level

Senior

Education Level

Associate degree

The resume builder that gets results.

Common questions about Physical Design Engineer careers and jobs.